Со 2 по 6 января пройдёт еще одна пресс-конференция International Electron Devices Meeting (IEDM 2017). По традиции руководители области по подготовке и изготовлению полупроводников поведают о достоинствах и прольют свет на значительные нюансы грядущих техпроцессов. Повестка главных представлений размещена, и у нас есть возможность осознать, о чём пойдёт диалог.

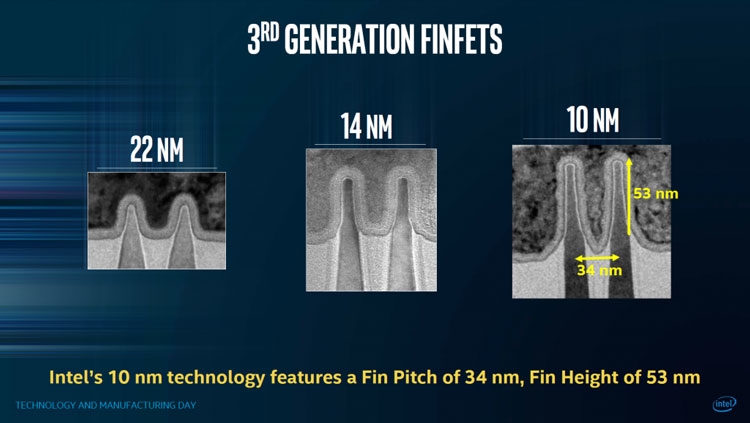

Так, организация Intel отдаст главное время отчету о фирменном техпроцессе с общепризнанными мерками 10 hm. известно, что габариты FinFET-транзисторов в техпроцессе Intel будут следующими: высота рёбер (транзисторных телеканалов) равна 7 hm, отдаление между районами рёбер составит 34 hm (pitch), но высота рёбер будет равна 46 hm (по иным данным — 53 hm). Для образования на кристалле частей такого объема организация применяет четырёхкратную проекцию с самовыравниванием фотошаблонов. Также Intel поведает о технологии изготовления высокоплотных и энергоэффективных ячей SRAM площадью 0,0312 мкм2 и 0,0441 мкм2 (на примере квалифицированного 204-Мбит массива SRAM).

Габариты рёбер FinFET транзисторов в 10-нм техпроцессе Intel (Intel)

Со слов Intel, 10-нм процесс разрешает образование 12 металлизированных межконтактных слоёв с помощью целого диапазона пороговых усилий. Сравнивая с 14-нм техпроцессом компании процесс с общепризнанными мерками 10 hm позволит повысить канальные флюиды для n-каналов транзисторов на 71 %, но для p-каналов — на 35 %. Помимо этого в 2-ух нижних пластах металлизации Intel будет применять токопроводящие дорожки из кобальта. Это вдесятеро усовершенствует положение дел с электромиграцией и вдвое понизит противодействие межслойной металлизации. Иными словами, кобальт снабдит надежность данных чипов и понизит токовую нагрузку на межслойные объединения.

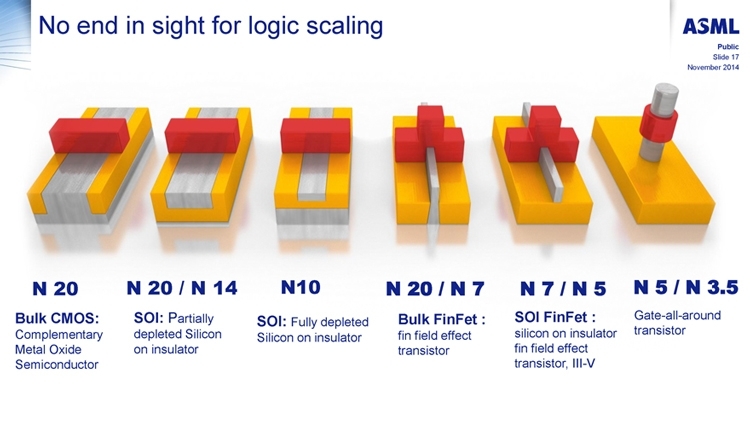

Виды важных и грядущих транзисторных строений (ASML)

Организация GlobalFoundries поделится достижениями в разработке ячеи SRAM площадью 0,0269 мкм2, что стало вероятно благодаря 7-нм техпроцессу с применением транзисторов FinFET. Сравнивая с 14-нм техпроцессом процесс GlobalFoundries с общепризнанными мерками 7 hm гарантирует 2,8-кратное повышение насыщенности расположения частей на кристалле и или не менее чем 40-процентный рост мощности, или 55-процентное падение употребления. Как и организация Intel, GlobalFoundries будет применять 4 проекции для производства кристаллов и 2 проекции для производства межслойных объединений. Этот процесс GlobalFoundries проектировала собственноручно, впрочем 14-нм процесс лицензировала у «Самсунг».

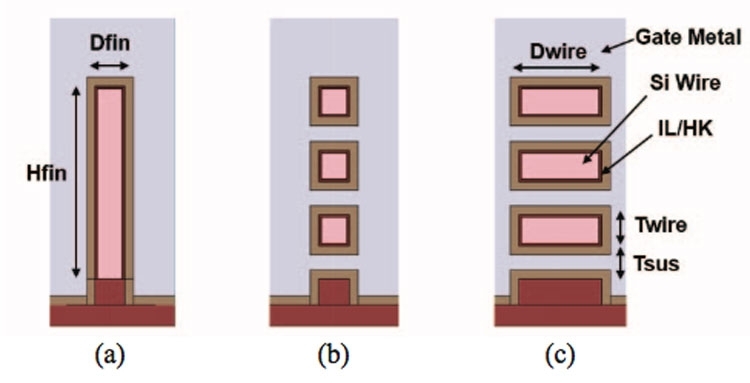

Телеканалы транзисторов обратятся в «перемычки» из нанопроводов и наностраниц (изображение IBM)

Помимо обозначенных организаций на пресс-конференции IEDM с любопытными докладами выступят представители Imec (речь пойдёт о свежих видах телеканалов транзисторов — целиком окружённых затворами, заключающимися из нанопроводов и наностраниц), организация Macronix поведает о фирменной памяти 3D NAND, организация SK Hynix порадует отчетом о памяти ReRAM, организация IBM и организация CEA-Leti отдельно поведают о 3D-компоновке цельной логики, ученые из Швеции продемонстрируют, как можно получать биоматериал из следа на примере чипов на пластинках FD-SOI, бригада из Houston Methodist Research Institute продемонстрирует как контролировать уровень средства в организме и получать гены при помощи чипов с микроканалами, но ученые из Техасского Института в Остине распределятся достижениями в изготовлении эластичной электроники из графена на стандартной бумаге. Ждём деталей.

Декабрь 15th, 2023

Декабрь 15th, 2023  raven000

raven000  Опубликовано в рубрике

Опубликовано в рубрике